I finally got around to putting the hardware together for my 8 bit adder project, as well as the Verilog for the FPGA.

Here is the working hardware setup:

Here are the three displays, one (Right) with the output, and two (Left, split half way) with the input.

Here is the Verilog that is running on the FPGA (Note, there are easier ways to implement this, I just wanted to do it “gatewise”):

-------------------------------------------------------------

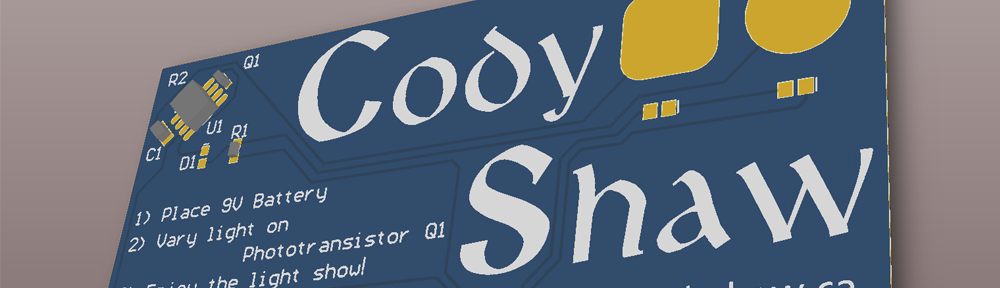

//Cody Shaw, 1B EE, University of Waterloo, 2012

module EightBitAdder(

//////////// CLOCK //////////

CLOCK_50,

//////////// GPIO_0, GPIO_0 connect to GPIO Default //////////

GPIO1,

GPIO1_IN,

//////////// GPIO_1, GPIO_1 connect to GPIO Default //////////

GPIO2,

GPIO2_IN

);

//////////// CLOCK //////////

input CLOCK_50;

//////////// GPIO_0, GPIO_0 connect to GPIO Default //////////

inout [33:0] GPIO1;

input [1:0] GPIO1_IN;

//////////// GPIO_1, GPIO_1 connect to GPIO Default //////////

inout [33:0] GPIO2;

input [1:0] GPIO2_IN;

//GPIO1_024 = End Carry

//GPIO1_00 -> 07 = Output

//GPIO1_08 -> 15 = Input Number 1

//GPIO1_16 -> 23 = Input Number 2

wire CARRY[7:0];

onebitadder adder0 (GPIO1[08],GPIO1[16],0,GPIO1[0],CARRY[0]); //So many adds!

onebitadder adder1 (GPIO1[09],GPIO1[17],CARRY[0],GPIO1[1],CARRY[1]);

onebitadder adder2 (GPIO1[10],GPIO1[18],CARRY[1],GPIO1[2],CARRY[2]);

onebitadder adder3 (GPIO1[11],GPIO1[19],CARRY[2],GPIO1[3],CARRY[3]);

onebitadder adder4 (GPIO1[12],GPIO1[20],CARRY[3],GPIO1[4],CARRY[4]);

onebitadder adder5 (GPIO1[13],GPIO1[21],CARRY[4],GPIO1[5],CARRY[5]);

onebitadder adder6 (GPIO1[14],GPIO1[22],CARRY[5],GPIO1[6],CARRY[6]);

onebitadder adder7 (GPIO1[15],GPIO1[23],CARRY[6],GPIO1[7],CARRY[7]);

assign GPIO1[24] = CARRY[7]; //Assign the carry bit to the 9th output bit

endmodule

module onebitadder (A, B, C, S, Co); //This module does the actual add functionality in terms of gates

input A;

input B;

input C;

output S;

output Co;

assign S = A^(B^C);

assign Co = (A&(B^C)) | (B&C);

endmodule

-------------------------------------------------------------

And that is it! I really enjoyed this project, I’ll have to think something up that is more difficult and interesting with my FPGA!

Best,

Cody